#### 1 Features

- Operating Frequency Band 2.40 GHz~2.48GHz unlicensed ISM Band

- Bluetooth Spec. v2.0 Compliant + EDR

- Enhanced Data Rate (EDR) compliant with v2.0.E.2 of specification for both 2Mbps and 3Mbps modulation modes

- Class 2 type Output Power

- Support Firmware Upgrade

- Support Piconet, up to 7 Slaves

- Scatternet Support

- USB 2.0 and UART Host Interface

- PCM Audio Interface

- Low Voltage Power Supply, 2.7V to 3.6V

- Nominal Supply Voltage at 3.3±0.1V

- Built-in 8Mbit Flash Memory

- Low Power Modes Available: Park, Sniff, Hold and Deep Sleep

- Surface-mount, Size: 27.0\*14.5\*1.8 mm

### 2 Product Description

The BC04 Bluetooth Module is a Class 2 Bluetooth module using BlueCore4-External chipset from leading Bluetooth chipset supplier, Cambridge Silicon Radio. It provides a fully compliant Bluetooth system for data and voice communications. Interfaces with a host via USB or UART and support full data rate up to 3Mbps modulation modes. Voice interface supported PCM protocol. The module and device firmware is fully compliant with the Bluetooth specification v2.0.

#### 3 Applications

- PCs, PDAs

- Computer Accessories (CF Cards, USB DonglesPCMCIA, RS232 Adaptors, etc.)

- Mice, Keyboard, Joysticks

- Cordless Phone

- FAX, Printer Adaptors

- Digital Camera

- Access Points to LAN and/or Dial-up network

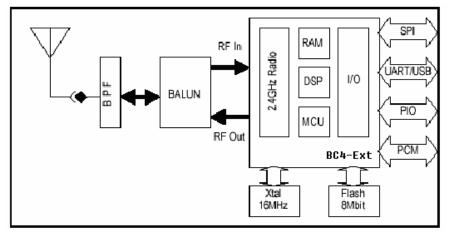

#### 4 Block Diagram

## 5 Pin Descriptions

| <u> </u> |              |                                       |                                                                            |

|----------|--------------|---------------------------------------|----------------------------------------------------------------------------|

| PIN      | NAME         | ŤYPE                                  | DESCRIPTION                                                                |

| 1        | GND          | GND                                   | Ground                                                                     |

| 2        | P109         | Bi-directional with programmable      | Programmable Input/Output Line                                             |

|          |              | strength internal pull-up/down        |                                                                            |

| 3        | GND          | GND                                   | Ground                                                                     |

| 4        | A100         | Bi-directional                        | Programmable input/output line                                             |

| 5        | P108         | Bi-directional with programmable      | Programmable Input/Output Line                                             |

|          |              | strength internal pull-up/down        |                                                                            |

| _        |              |                                       | internal pull-up Reset if low. Input                                       |

| 6        | RESETB       | CMOS input with weakinternal pull-up  | debounced so must be low for >5ms to                                       |

|          |              |                                       | cause a reset                                                              |

| 7        | SPI_MISO     | CMOS output, tri-state, with weak     | Serial Peripheral Interface data                                           |

|          |              | internal pull-down                    | output                                                                     |

| 8        | SPI_CSB      | CMOS input with weak internal pull-up | Chip select for Synchronous Serial                                         |

| -        | _            |                                       | Interface active low                                                       |

| 9        | SPI_CLK      | CMOS input with weak internal         | Serial Peripheral Interface clock                                          |

|          |              | pull-down                             |                                                                            |

| 10       | SPI_MOSI     | CMOS input with weak internal         | Serial Peripheral Interface data                                           |

|          |              | pull-down                             | input                                                                      |

| 11       | UART_CTS     | CMOS input with weak                  | UART clear to send active low                                              |

|          | _            | internal pull-down                    |                                                                            |

| 12       | UART_TX      | CMOS output, tri-state, with weak     | UART data output                                                           |

|          |              | internal pull-up                      |                                                                            |

|          |              | CMOS output, tri-state, with weak     | UART request to send active low                                            |

| 13       | UART_RTS     | internal pull-up                      | · · · · · · · · · · · · · · · · · · ·                                      |

|          |              |                                       |                                                                            |

| 14       | UART_RX      | CMOS input with weak internal         | UART data input                                                            |

|          |              | pull-down                             |                                                                            |

| 15       | 1.8V Filter  |                                       | Filter Capacitor for 1.8V                                                  |

|          |              |                                       | +3.3V Power Supply. Since the big<br>DC/DC ripple, using the LDO to supply |

| 16       | VDD          | Power Supply                          | but but ripple, using the LDO to supply                                    |

|          |              |                                       | the power to module is required, or the distance will be affected.         |

|          |              |                                       | the distance with be allected.                                             |

| 17       | NC           |                                       | Do Not Connect This Pin                                                    |

| 18       | AI01         | Bi-directional                        | Programmable input/output line                                             |

| 19       | A102         | Bi-directional                        | Programmable input/output line                                             |

| 20       | PI011        | Bi-directional with programmable      | Programmable Input/Output Line                                             |

|          |              | strength internal pull-up/down        |                                                                            |

| 21       | PI010        | Bi-directional with programmable      | Programmable Input/Output Line                                             |

|          |              | strength internal pull-up/down        |                                                                            |

| 22       | PCM_OUT      | CMOS output, tri-state, with weak     | Synchronous data output                                                    |

|          |              | internal pull-down                    |                                                                            |

| 23       | PCM_SYNC     | Bi-directional with weak internal     | Synchronous data sync                                                      |

|          |              | pull-down                             |                                                                            |

| 24       | PCM_IN       | CMOS input, with weak internal        | Synchronous data input                                                     |

|          |              | pull-down                             |                                                                            |

| 25       | PCM_CLK      | Bi-directional with weak              | Synchronous data clock                                                     |

|          |              | internal pull-down                    |                                                                            |

| 26       | USB_DP       | Bi-directional                        | USB data plus with selectable                                              |

| -        |              |                                       | internal 1.5k. pull-up resistor                                            |

| 27       | USB_DM       | Bi-directional                        | USB data minus                                                             |

| 28       | P107         | Bi-directional with programmable      | Programmable Input/Output Line                                             |

|          |              | strength internal pull-up/down        | ~ · ·                                                                      |

| 29       | PI0[6]/      | Bi-directional with programmable      | Programmable input/output line or                                          |

|          | WLAN_Active/ | strength internal pull-up/down        | Optionally WLAN_Active/Ch_Data input                                       |

| L        |              | <b>· ·</b> · · · · ·                  |                                                                            |

| -  |                                   |                                                                 |                                                                                                          |

|----|-----------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|    | Ch_Data                           |                                                                 | for co-existence signalling                                                                              |

| 30 | PIO[5]/<br>BT_Active              | Bi-directional with programmable strength internal pull-up/down | Programmable input/output line or<br>Optionally BT_Active output for<br>co-existence signalling          |

| 31 | PIO[4]/<br>BT_Priority/<br>Ch_Clk | Bi-directional with programmable strength internal pull-up/down | Programmable input/output line or<br>Optionally BT_Priority/Ch_Clk output<br>for co-existence signalling |

| 32 | P103                              | Bi-directional with programmable strength internal pull-up/down | Programmable Input/Output Line                                                                           |

| 33 | P102                              | Bi-directional with programmable strength internal pull-up/down | Programmable Input/Output Line                                                                           |

| 34 | PI01                              | Bi-directional with programmable strength internal pull-up/down | Programmable Input/Output Line                                                                           |

| 35 | P100                              | Bi-directional with programmable strength internal pull-up/down | Programmable Input/Output Line                                                                           |

| 36 | GND                               | GND                                                             | Ground                                                                                                   |

### 6 Electrical Specifications 6.1 Electrical Characteristics

Input/Output Terminal Characteristics

| Digital Terminals                       | Min     | Тур  | Max     | Unit |  |  |  |

|-----------------------------------------|---------|------|---------|------|--|--|--|

| Input Voltage Levels                    |         |      |         |      |  |  |  |

| VIL input logic level low 2.7V VDD 3.0V | -0.4    | -    | +0.8    | V    |  |  |  |

| VIH input logic level high              | 0.7VDD  | -    | VDD+0.4 | V    |  |  |  |

| Output Voltage Levels                   |         |      |         |      |  |  |  |

| VOL output logic level low              | -       | -    | 0.2     | V    |  |  |  |

| (Io = 4.0mA), 2.7V VDD 3.0V             |         |      |         |      |  |  |  |

| VOH output logic level high             | VDD-0.2 | -    | -       | V    |  |  |  |

| (Io = -4.0mA), 2.7V VDD 3.0V            |         |      |         |      |  |  |  |

| Input and Tri-state Current with        |         |      |         |      |  |  |  |

| Strong pull-up                          | -100    | -40  | -10     | μA   |  |  |  |

| Strong pull-down                        | +10     | +40  | +100    | μA   |  |  |  |

| Weak pull-up                            | -5.0    | -1.0 | -0.2    | μA   |  |  |  |

| Weak pull-down                          | +0.2    | +1.0 | +5.0    | μA   |  |  |  |

| I/O pad leakage current                 | -1      | 0    | +1      | μA   |  |  |  |

| CI Input Capacitance                    | 1.0     | -    | 5.0     | pF   |  |  |  |

#### Input/Output Terminal Characteristics(Continued)

| USB Terminals                                           | Min        | Тур | Max        | Unit |  |  |  |

|---------------------------------------------------------|------------|-----|------------|------|--|--|--|

| VDD_USB for correct USB operation(1)                    | 3.1        | -   | 3.6        | V    |  |  |  |

| Input threshold                                         |            |     |            |      |  |  |  |

| VIL input logic level low                               | -          | -   | 0.3VDD_USB | V    |  |  |  |

| VIH input logic level high                              | 0.7VDD_USB | -   | -          | V    |  |  |  |

| Input leakage current                                   |            |     |            |      |  |  |  |

| VSS_PADS < VIN < VDD_USB(1)                             | -1         | 1   | 5          | μA   |  |  |  |

| CI Input capacitance                                    | 2.5        | -   | 10.0       | pF   |  |  |  |

| Output Voltage levels To correctly terminated USB Cable |            |     |            |      |  |  |  |

| VOL output logic level low                              | 0.0        | -   | 0.2        | V    |  |  |  |

| VOH output logic level high                             | 2.8        | -   | VDD_USB    | V    |  |  |  |

#### Notes:

(1) Let VDD voltage higher than common appliance, when USB works

### 6.2 Absolute Maximum ratings

Absolute maximum ratings for supply voltage and voltages on digital and analogue pins of the Module are listed below; exceeding these values will cause permanent damage.

| Parameter                    | Min  | Max | Unit |

|------------------------------|------|-----|------|

| Peak current of power supply | 0    | 75  | mA   |

| Voltage at digital pins      | -0.3 | 3.6 | V    |

| Voltage at POWER pin         | 2.7  | 3.6 | V    |

#### 6.3 Power Consumption

| Operation Mode             | Connection | UART Rate   | Average | Unit |  |

|----------------------------|------------|-------------|---------|------|--|

| ·                          | Туре       | Type (kbps) |         |      |  |

| Page scan                  | -          | 115.2       | 0.42    | mA   |  |

| Inquiry and page scan      | -          | 115.2       | 0.76    | mA   |  |

| ACL No traffic             | Master     | 115.2       | 4.60    | mA   |  |

| ACL With file transfer     | Master     | 115.2       | 10.3    | mA   |  |

| ACL No traffic             | Slave      | 115.2       | 17.0    | mA   |  |

| ACL With file transfer     | Slave      | 115.2       | 24.7    | mA   |  |

| ACL 40ms sniff             | Master     | 38.4        | 2.40    | mA   |  |

| ACL 1.28s sniff            | Master     | 38.4        | 0.37    | mA   |  |

| SCO HV1                    | Master     | 38.4        | 39.2    | mA   |  |

| SCO HV3                    | Master     | 38.4        | 20.3    | mA   |  |

| SCO HV3 30ms sniff         | Master     | 38.4        | 19.8    | mA   |  |

| ACL 40ms sniff             | Slave      | 38.4        | 2.11    | mA   |  |

| ACL 1.28s sniff            | Slave      | 38.4        | 0.42    | mA   |  |

| Parked 1.28s beacon        | Slave      | 38.4        | 0.20    | mA   |  |

| SCO HV1                    | Slave      | 38.4        | 39.1    | mA   |  |

| SCO HV3                    | Slave      | 38.4        | 24.8    | mA   |  |

| SCO HV3 30ms sniff         | Slave      | 38.4        | 19.0    | mA   |  |

| Standby Host connection(a) | -          | 38.4        | 40      | uA   |  |

| Reset (RESETB low)(a)      | -          | -           | 34      | uA   |  |

(a) Low power mode on the linear regulator is entered and exited automatically when the chip enters/leaves Deep Sleep mode .

#### 7 DC Characteristics

#### 7.1 RF Performance

# 7.1.1 Transmit Power

|                                 | Min | Тур | Max | Bluetooth     | Unit |  |

|---------------------------------|-----|-----|-----|---------------|------|--|

|                                 |     |     |     | Specification |      |  |

| Maximum RF transmit power(1)(2) | -   | 2.5 | -   | -6 to +4(3)   | dBm  |  |

Notes:

(1) BlueCore4 firmware maintains the transmit power to be within the Bluetooth v2.0 + EDRspecification limits.

(2) Measurement made using a PSKEY\_LC\_MAX\_TX\_POWER setting corresponds to a PSKEY\_LC\_POWER\_TABLE power table entry of 63.

(3) Class 2 RF transmit power range, Bluetooth v2.0 + EDR specification.

| Temperature = +20 °C                |                |     |     |     |               |      |  |

|-------------------------------------|----------------|-----|-----|-----|---------------|------|--|

|                                     | Frequency(GHz) | Min | Тур | Max | Bluetooth     | Unit |  |

|                                     |                |     |     |     | Specification |      |  |

| Sensitivity                         | 2.402          | -   | -84 | -   | -             | i    |  |

| at 0.1% BER for                     | 2.441          | -   | -84 | -   | -70           | dBm  |  |

| all packet types                    | 2.480          | -   | -85 | -   |               |      |  |

| Maximum received signal at 0.1% BER |                | -   | 10  | -   | -20           | dBm  |  |

#### 7.1.2 Receiver Sensitivity

#### 8 Solder Profiles

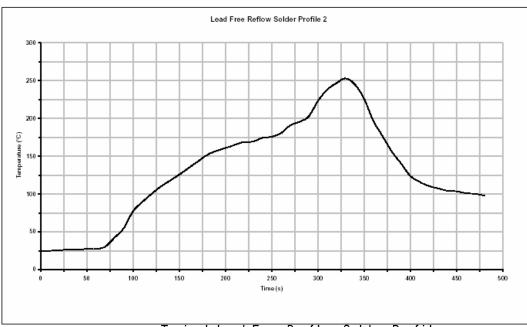

The soldering profile depends on various parameters necessitating a set up for each application. The data here is given only for guidance on solder re-flow. There are four zones:

1.Preheat Zone - This zone raises the temperature at a controlled rate, typically 1-2.5  $^\circ$  C/s.

2.Equilibrium Zone - This zone brings the board to a uniform temperature and also activates the flux.

The duration in this zone (typically 2-3 minutes) will need to be adjusted to optimise the out gassing of the flux.

3.Reflow Zone - The peak temperature should be high enough to achieve good wetting but not so high as to cause component discoloration or damage. Excessive soldering time can lead to intermetallic growth which can result in a brittle joint.

4.Cooling Zone - The cooling rate should be fast, to keep the solder grains small which will give a longer lasting joint. Typical rates will be 2-5 ° C/s.

8.1 Solder Re-Flow Profile

Typical Lead-Free Re-flow Solder Profile

Key features of the profile:

- Initial Ramp = 1-2.5 °C/sec to 175 °C±25 °C equilibrium

- Equilibrium time = 60 to 180 seconds

- Ramp to Maximum temperature (250 °C) = 3 °C/sec max.

- Time above liquidus temperature (217 °C): 45-90 seconds

- Device absolute maximum reflow temperature: 260 ° C

Devices will withstand the specified profile. Lead-free devices will withstand up to three reflows to a maximum temperature of 260 °C.

Notes: They need to be baked prior to mounting.

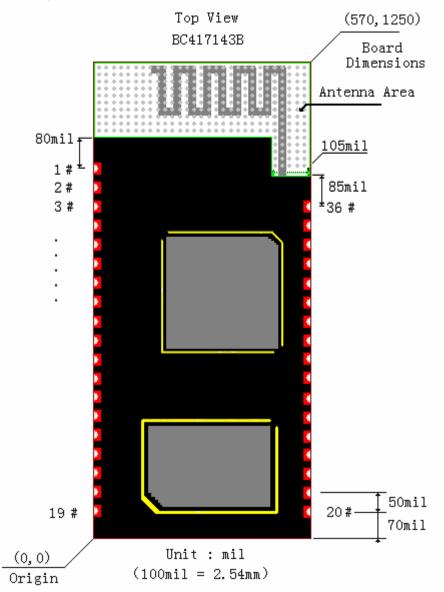

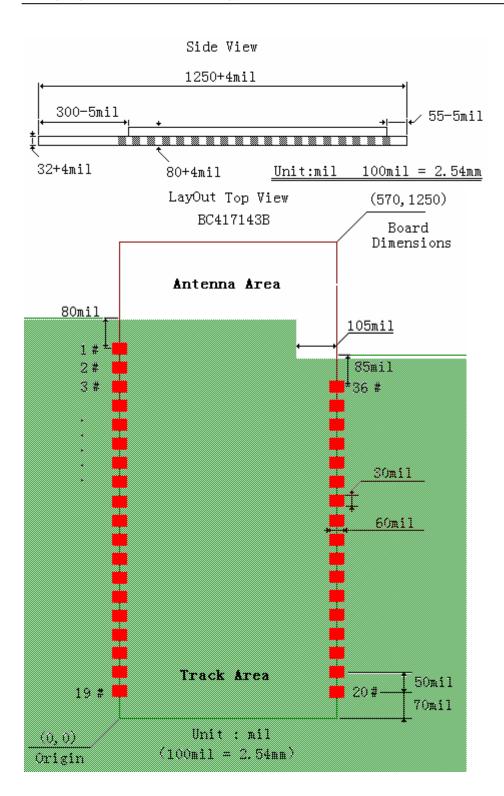

#### 9 Physical Dimensions

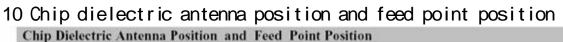

Below this, trying to let metal line be inexistent.

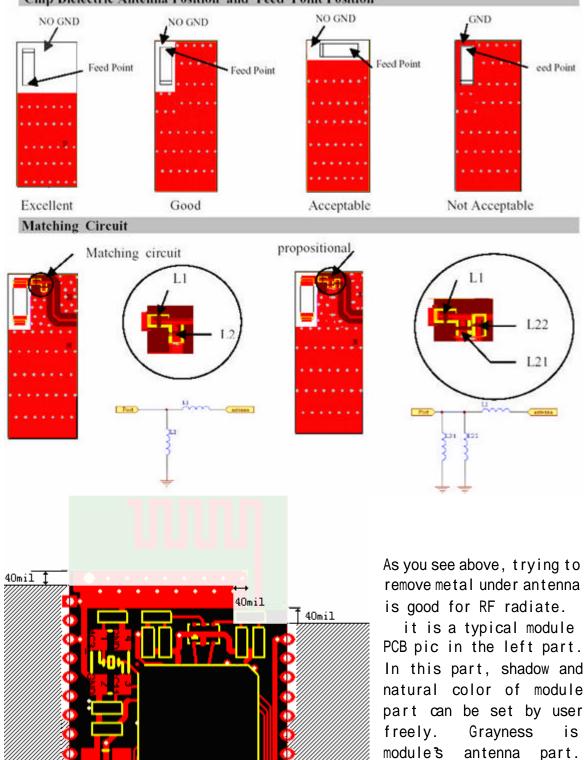

# 11 Check List (refer to SCHpic)

#### 11.1 Sch Check List

Function voltage of the module power is 2.7 to 3.6V. so the RS232 chipset needs to be transfer is also applied to this voltage bound. This typical component is MAX3232. but we should pay a attention on MAX3232 function baud rate, which is 120kbps.

pic adopt stable voltage chipset, the highest voltage is 12V.SCH. obviously, module should be broken if beyond this bound. This chipset fall into lower-voltage chipset, we suggest adopting external power in the range of 5 0.25v.

From above USB power supply list, we can get once we use USB, the best way is trying to let module work on the range of  $3.3 \quad 0.1 \text{ V}$ .

#### **11.2 PCB Check List**

• antenna part(RF part) is close to device edge to the greatest extent, there must be without any metal obstruct between the direction of antenna energy radiate and outside. Check more details in 10 Chip dielectric antenna position and feed point position "?

• the bottom of module touch PCB. in order to eliminate capable short circuit, try to use insulation material separating two side of metal in setting module part. Simple way, place a holistic silk-screen here.

• considering about integer beauty impression on the base of compliance to electric product and mechanism configuration requirement, component setting must be equilibria and density in order on PCB.

• PCB dimension must be similar to machining drawing, and accord with PCB manufacturing craftwork request. try to make sure there isn t any conflict in two dimension space or three dimension when we set MARK point here.

• component need replacing frequently ask for convenient insert board. UART with direction adopt dissymmetric UART mark.

• though current module we use right now isn t hot-sensitive component, we also need proper distance between two components.

• setting line must have logical direction. For example, input/ output, AC/DC, strong/weak singal, high/ low frequency, high/ low voltage and so on, their direction should be a line (or separated) not mingle with another, in order to avoid disturbing each other. The best setting direction is compliant to line, but it is hard to realize.

• logically set power strain wave/capacitance. Try to be close to these components in setting capacitance. If the distance is too far it canf function well.

## 12 Figure

ChongQing JINOU Science & Technology Co.,LTD Tel: +86-23-68798999 Fax: +86-23-68889515 Add: ChongQing JINOU Science & Technology Co.,LTD, GuiGu City Villa 12-2-101, Huaxuan Branch108# Yuzhou Road, Hi-Tech Development Zone, Chongqing, China Website: www.OEMblue.com